# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

# Low Power + Quad 256-tap + 2-Wire Bus + Up/Down Interface

Data Sheet July 24, 2014 FN8167.3

# Quad Digitally-Controlled (XDCP™) Potentiometer

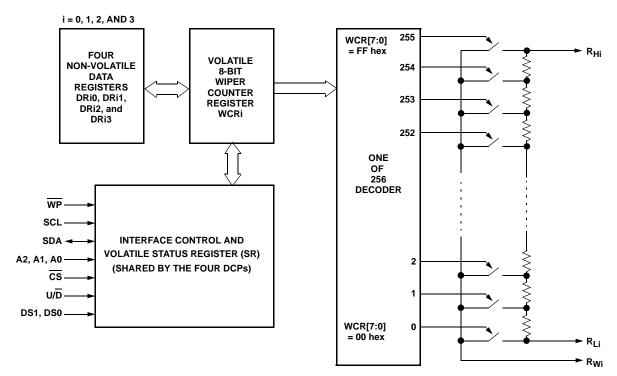

The X9252 integrates 4 digitally controlled potentiometers (XDCP) on a monolithic CMOS integrated circuit.

The digitally controlled potentiometers are implemented using 255 resistive elements in a series array. Between each pair of elements are tap points connected to wiper terminals through switches. The position of each wiper on the array is controlled by the user through the Up/Down (U/ $\overline{D}$ ) or 2-wire bus interface. The wiper of each potentiometer has an associated volatile Wiper Counter Register (WCR) and four nonvolatile Data Registers (DRs) that can be directly written to and read by the user. The contents of the WCR controls the position of the wiper on the resistor array through the switches. At power-up, the device recalls the contents of the default data registers DR00, DR10, DR20, DR30, to the corresponding WCR.

Each DCP can be used as a three-terminal potentiometer or as a two terminal variable resistor in a wide variety of applications including the programming of bias voltages, the implementation of ladder networks, and three resistor programmable networks.

#### **Features**

- · Quad Solid State Potentiometer

- 256 Wiper Tap Points-0.4% Resolution

- 2-Wire Serial Interface for Write, Read, and Transfer Operations of the Potentiometer

- · Up/Down Interface for Individual Potentiometers

- Wiper Resistance: 40Ω Typical

- NonVolatile Storage of Wiper Positions

- Power On Recall. Loads Saved Wiper Position on Power-Up.

- Standby Current < 100µA Max</li>

- Maximum Wiper Current: 3mA

- V<sub>CC</sub>: 2.7V to 5.5V Operation

- 2.8kΩ and 10kΩ Version of Total Pot Resistance

- Endurance: 100,000 Data Changes per Bit per Register

- 100 yr. Data Retention

- 24 Ld TSSOP

- · Pb-Free (RoHS Compliant)

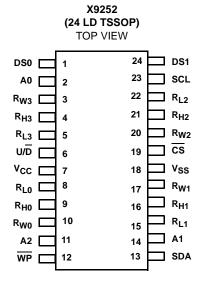

#### **Pinout**

# **Ordering Information**

| PART<br>NUMBER<br>( <u>Notes 1</u> , <u>2</u> ) | PART<br>MARKING | R <sub>TOTAL</sub><br>(kΩ) | TEMP RANGE<br>(°C) | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |

|-------------------------------------------------|-----------------|----------------------------|--------------------|----------------------|----------------|

| X9252YV24IZ-2.7                                 | X9252YV ZG      | 2.8                        | -40 to +85         | 24 Ld TSSOP (4.4mm)  | M24.173        |

| X9252WV24IZ-2.7                                 | X9252WV ZG      | 10                         | -40 to +85         | 24 Ld TSSOP (4.4mm)  | M24.173        |

#### NOTES:

- 1. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 2. For Moisture Sensitivity Level (MSL), please see device information page for X9252. For more information on MSL please see tech brief TB363

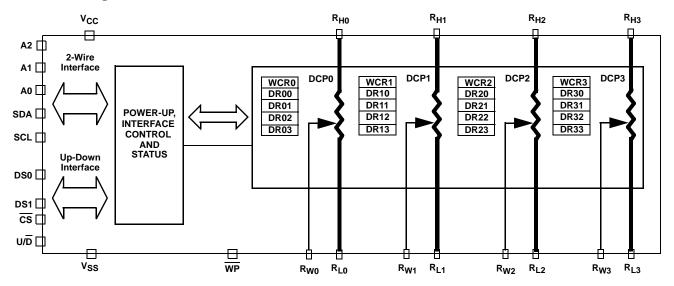

# Functional Diagram

# Pin Descriptions

| PIN#      | SYMBOL          | DESCRIPTION                                |

|-----------|-----------------|--------------------------------------------|

| 1, 24     | DS0, DS1        | DCP select for Up/Down interface.          |

| 2, 14, 11 | A0, A1, A2      | Device address for 2-wire bus.             |

| 3         | R <sub>W3</sub> | Wiper terminal of DCP3.                    |

| 4         | R <sub>H3</sub> | High terminal of DCP3.                     |

| 5         | R <sub>L3</sub> | Low terminal of DCP3.                      |

| 6         | U/D             | Increment/decrement for up/down interface. |

| 7         | Vcc             | System supply voltage                      |

| 8         | R <sub>L0</sub> | Low terminal of DCP0.                      |

| 9         | R <sub>H0</sub> | High terminal of DCP0.                     |

| 10        | R <sub>W0</sub> | Wiper terminal of DCP0.                    |

| 12        | WP              | Hardware write protect                     |

| 13        | SDA             | Serial data input/output for 2-wire bus.   |

| 15        | R <sub>L1</sub> | Low terminal of DCP1.                      |

| 16        | R <sub>H1</sub> | High terminal of DCP1.                     |

| 17        | R <sub>W1</sub> | Wiper terminal DCP1.                       |

| 18        | V <sub>SS</sub> | System ground                              |

Submit Document Feedback intersil FN8167.3 July 24, 2014

## Pin Descriptions (Continued)

| PIN# | SYMBOL          | DESCRIPTION                        |

|------|-----------------|------------------------------------|

| 19   | CS              | Chip select for Up/Down interface. |

| 20   | R <sub>W2</sub> | Wiper terminal of DCP2.            |

| 21   | R <sub>H2</sub> | High terminal of DCP2.             |

| 22   | R <sub>L2</sub> | Low terminal of DCP2.              |

| 23   | SCL             | Serial clock for 2-wire bus.       |

# Pin Descriptions

#### **Bus Interface Pins**

#### Serial Data Input/Output (SDA)

The SDA is a bidirectional serial data input/output pin for the 2-wire interface. It receives device address, operation code, wiper register address and data from a 2-wire external master device at the rising edge of the serial clock SCL, and it shifts out data after each falling edge of the serial clock SCL.

SDA requires an external pull-up resistor, since it's an open drain output.

#### Serial Clock (SCL)

This input is the serial clock of the 2-wire and Up/Down interface.

### Device Address (A0, A1, A2)

The Address inputs are used to set the least significant 3 bits of the 8-bit 2-wire interface slave address. A match in the slave address serial data stream must be made with the Address input pins in order to initiate communication with the X9252. A maximum of 8 devices may occupy the 2-wire serial bus.

### Chip Select (CS)

When the  $\overline{CS}$  pin is low, increment or decrement operations are possible using the SCL and U/ $\overline{D}$  pins. The 2-wire interface is disabled at this time. When  $\overline{CS}$  is high, the 2-wire interface is enabled.

#### Up or Down Control (U/D)

The  $U/\overline{D}$  input pin is held HIGH during increment operations and held LOW during decrement operations.

#### DCP Select (DS1 and DS0)

The DS1 and DS0 select one of the four DCPs for an Up/Down interface operation.

### Hardware Write Protect Input (WP)

When the  $\overline{\text{WP}}$  pin is set low, "write" operations to nonvolatile DCP Data Registers are disabled. This includes both 2-wire interface nonvolatile "Write", and Up/Down interface "Store" operations.

#### **DCP Pins**

#### R<sub>H0</sub>, R<sub>L0</sub>, R<sub>H1</sub>, R<sub>L1</sub>, R<sub>H2</sub>, R<sub>L2</sub>, R<sub>H3</sub>, and R<sub>L3</sub>

These pins are equivalent to the terminal connections on mechanical potentiometers. Since there are 4 DCPs, there is one set of  $R_{H}$  and  $R_{I}$  for each DCP.

#### R<sub>W0</sub>, R<sub>W1</sub>, R<sub>W2</sub>, and R<sub>W3</sub>

The wiper pins are equivalent to the wiper terminal of mechanical potentiometers. Since there are four DCPs, there are 4  $R_{W}$  pins.

Submit Document Feedback 3 intersil\* FN8167.3

July 24, 2014

## **Absolute Maximum Ratings**

####

### **Recommended Operating Conditions**

| Industrial                                        | 40°C to +85°C    |

|---------------------------------------------------|------------------|

| Supply Voltage (V <sub>CC</sub> ) (Note 6) Limits | 2.7V to 5.5V     |

| Pb-Free Reflow Profile                            | see <u>TB493</u> |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

# Analog Specifications Across recommended operating conditions unless otherwise stated. Boldface limits apply across the operating temperature range, -40°C to +85°C.

| SYMBOL                                         | PARAMETER                                      | TEST CONDITIONS                                                                                                      | MIN<br>( <u>Note 12</u> ) | TYP<br>(Note 6) | MAX<br>( <u>Note 12</u> ) | UNIT                    |

|------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------|---------------------------|-------------------------|

| R <sub>TOTAL</sub>                             | End-to-End Resistance                          | Y, W versions respectively                                                                                           |                           | 2.8, 10         |                           | kΩ                      |

|                                                | End-to-End Resistance Tolerance                |                                                                                                                      | -20                       |                 | +20                       | %                       |

|                                                | Power Rating                                   | +25°C, each DCP                                                                                                      |                           |                 | 50                        | mW                      |

| R <sub>TOTAL</sub><br>Matching                 | DCP to DCP Resistance Matching                 |                                                                                                                      |                           | 0.75            | 2.0                       | %                       |

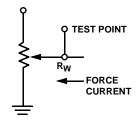

| I <sub>W</sub>                                 | Wiper Current (Note 7)                         | See <u>"Test Circuit" on page 8</u>                                                                                  | -3.0                      |                 | +3.0                      | mA                      |

| R <sub>W</sub>                                 | Wiper Resistance                               | Wiper current = $\frac{V_{CC}}{R_{TOTAL}}$                                                                           |                           | 50              | 150                       | Ω                       |

| V <sub>TERM</sub>                              | Voltage on any DCP Pin                         |                                                                                                                      | V <sub>SS</sub>           |                 | v <sub>cc</sub>           | V                       |

|                                                | Noise (Note 7)                                 | Ref: 1kHz                                                                                                            |                           | -120            |                           | dBV                     |

|                                                | Resolution                                     |                                                                                                                      |                           | 0.4             |                           | %                       |

|                                                | Absolute Linearity (Note 3)                    | $V(R_{H0}) = V(R_{H1}) = V(R_{H2}) = V(R_{H3}) = V_{CC}$<br>$V(R_{L0}) = V(R_{L1}) = V(R_{L2}) = V(R_{L3}) = V_{SS}$ | -1                        |                 | +1                        | MI<br>( <u>Note 5</u> ) |

|                                                | Relative linearity (Note 4)                    |                                                                                                                      | -0.3                      |                 | +0.3                      | MI<br>( <u>Note 5</u> ) |

|                                                | Temperature coefficient of resistance (Note 7) |                                                                                                                      |                           | ±300            |                           | ppm/°C                  |

|                                                | Ratiometric Temperature (Note 7) Coefficient   |                                                                                                                      | -20                       |                 | +20                       | ppm/°C                  |

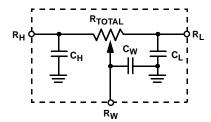

| C <sub>H</sub> /C <sub>L</sub> /C <sub>W</sub> | Potentiometer Capacitance (Note 7)             | See "Equivalent Circuit" on page 8                                                                                   |                           | 10/10/25        |                           | pF                      |

| l <sub>OL</sub>                                | Leakage on DCP Pins                            | Voltage at pin from V <sub>SS</sub> to V <sub>CC</sub>                                                               |                           | 0.1             | 10                        | μA                      |

# DC Electrical Specifications Across the recommended operating conditions unless otherwise specified. Boldface limits apply across the operating temperature range, -40°C to +85°C.

| SYMBOL           | PARAMETER                                            | TEST CONDITIONS                                                                                       | MIN<br>(Note 12)      | MAX<br>(Note 12)      | UNITS |

|------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-------|

| I <sub>CC1</sub> | V <sub>CC</sub> Supply Current (Volatile Write/Read) | f <sub>SCL</sub> = 400kHz; SDA = open; (for 2-wire, active, read and volatile write states only)      |                       | 3                     | mA    |

| I <sub>CC2</sub> | V <sub>CC</sub> Supply Current (Active)              | f <sub>SCL</sub> = 200kHz;<br>(for U/D interface, increment, decrement)                               |                       | 3                     | mA    |

| I <sub>CC3</sub> | V <sub>CC</sub> Supply Current (Nonvolatile Write)   | f <sub>SCL</sub> = 400kHz; SDA = Open;<br>(for 2-wire, active, nonvolatile write state only)          |                       | 5                     | mA    |

| I <sub>SB</sub>  | V <sub>CC</sub> Current (Standby)                    | $V_{CC}$ = +5.5V; $V_{IN}$ = $V_{SS}$ or $V_{CC}$ ; SDA = $V_{CC}$ ; (for 2-Wire, standby state only) |                       | 100                   | μΑ    |

| IL               | Leakage Current, Bus Interface Pins                  | Voltage at pin from V <sub>SS</sub> to V <sub>CC</sub>                                                | -10                   | 10                    | μA    |

| V <sub>IH</sub>  | Input HIGH Voltage                                   |                                                                                                       | V <sub>CC</sub> x 0.7 | V <sub>CC</sub> + 1   | V     |

| V <sub>IL</sub>  | Input LOW Voltage                                    |                                                                                                       | -1                    | V <sub>CC</sub> x 0.3 | V     |

| V <sub>OL</sub>  | SDA Pin Output LOW Voltage                           | I <sub>OL</sub> = 3mA                                                                                 |                       | 0.4                   | V     |

Submit Document Feedback 4 intersil 5 FN8167.3 July 24, 2014

# **Endurance and Data Retention**

| PARAMETER         | MIN     | UNITS                |

|-------------------|---------|----------------------|

| Minimum Endurance | 100,000 | Data changes per bit |

| Data Retention    | 100     | Years                |

# Capacitance

| Symbol                       | Test                                                                                                     | Test Conditions      | Max | UNITS |

|------------------------------|----------------------------------------------------------------------------------------------------------|----------------------|-----|-------|

| C <sub>IN/OUT</sub> (Note 7) | Input/Output Capacitance (SDA)                                                                           | $V_{OUT} = 0V$       | 8   | pF    |

| C <sub>IN</sub> (Note 7)     | Input Capacitance (SCL, $\overline{WP}$ , DS0, DS1, $\overline{CS}$ , U/ $\overline{D}$ , A2, A1 and A0) | V <sub>IN</sub> = 0V | 6   | pF    |

# **Power-Up Timing**

| SYMBOL                                | PARAMETER                                                                                                                                                       | MAX | UNITS |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| t <sub>D</sub> ( <u>Notes 7, 11</u> ) | Power-Up Delay from V <sub>CC</sub> Power-Up (V <sub>CC</sub> above 2.7V) to Wiper Position Recall Completed, and Communication Interfaces Ready for Operation. | 2   | ms    |

# **A.C. Test Conditions**

| Input Pulse Levels                      | V <sub>CC</sub> x 0.1 to V <sub>CC</sub> x 0.9                |

|-----------------------------------------|---------------------------------------------------------------|

| Input Rise and Fall Times               | 10ns                                                          |

| Input and Output Timing Threshold Level | V <sub>CC</sub> x 0.5                                         |

| External Load at Pin SDA                | 2.3k $\Omega$ to V <sub>CC</sub> and 100pF to V <sub>SS</sub> |

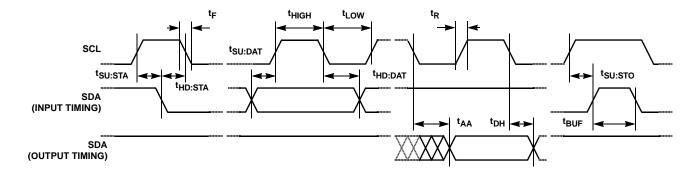

# 2-Wire Interface Timing (s)

| SYMBOL                       | PARAMETER                                          | MIN  | MAX | UNITS |

|------------------------------|----------------------------------------------------|------|-----|-------|

| f <sub>SCL</sub>             | Clock Frequency                                    |      | 400 | kHz   |

| tHIGH                        | Clock High Time                                    | 600  |     | ns    |

| t <sub>LOW</sub>             | Clock Low Time                                     | 1300 |     | ns    |

| t <sub>SU:STA</sub>          | Start Condition Setup Time                         | 600  |     | ns    |

| t <sub>HD:STA</sub>          | Start Condition Hold Time                          | 600  |     | ns    |

| t <sub>SU:STO</sub>          | Stop Condition Setup Time                          | 600  |     | ns    |

| t <sub>SU:DAT</sub>          | SDA Data Input Setup Time                          | 100  |     | ns    |

| t <sub>HD:DAT</sub>          | SDA Data Input Hold Time                           | 30   |     | ns    |

| t <sub>R</sub> (Note 7)      | SCL and SDA Rise Time                              |      | 300 | ns    |

| t <sub>F</sub> (Note 7)      | SCL and SDA Fall Time                              |      | 300 | ns    |

| t <sub>AA</sub> (Note 7)     | SCL Low to SDA Data Output Valid Time              |      | 0.9 | μs    |

| t <sub>DH</sub>              | SDA Data Output Hold Time                          | 0    |     | ns    |

| t <sub>IN</sub> (Note 7)     | Pulse Width Suppression Time at SCL and SDA inputs |      | 50  | ns    |

| t <sub>BUF</sub> (Note 7)    | Bus Free Time (Prior to Any Transmission)          | 1200 |     | ns    |

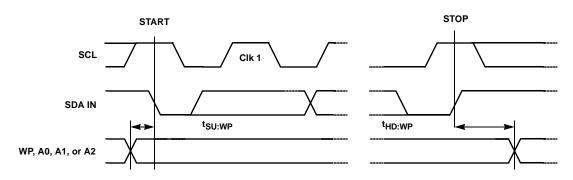

| t <sub>SU:WPA</sub> (Note 7) | A0, A1, A2 and WP Setup Time                       | 600  |     | ns    |

| t <sub>HD:WPA</sub> (Note 7) | A0, A1, A2 and WP Hold Time                        | 600  |     | ns    |

Submit Document Feedback 5 intersil\* FN8167.3

July 24, 2014

# SDA vs SCL Timing

WP, A0, A1, and A2 Pin Timing

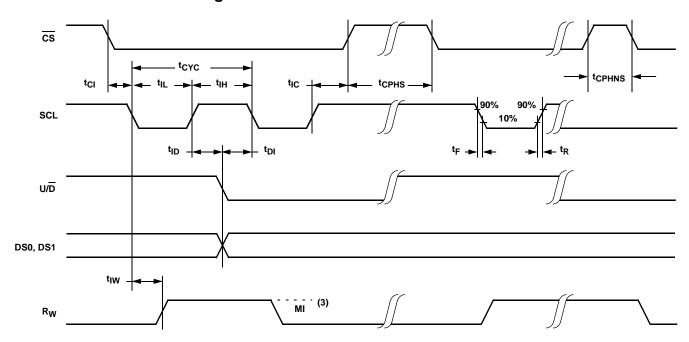

# **Increment/Decrement Timing**

| SYMBOL                                            | PARAMETER                                                  | MIN | TYP (Note 6) | MAX | UNITS |

|---------------------------------------------------|------------------------------------------------------------|-----|--------------|-----|-------|

| t <sub>Cl</sub>                                   | CS to SCL Setup                                            | 600 |              |     | ns    |

| t <sub>ID</sub> (Note 7)                          | SCL HIGH to U/D, DS0 or DS1 Change                         | 600 |              |     | ns    |

| t <sub>DI</sub> (Note 7)                          | U/D, DS0 or DS1 to SCL Setup                               | 600 |              |     | ns    |

| t <sub>IL</sub>                                   | SCL LOW Period                                             | 2.5 |              |     | μs    |

| t <sub>IH</sub>                                   | SCL HIGH Period                                            | 2.5 |              |     | μs    |

| t <sub>IC</sub>                                   | SCL Inactive to CS Inactive (Nonvolatile Store Setup Time) | 1   |              |     | μs    |

| tCPHS                                             | CS Deselect Time (Store)                                   | 10  |              |     | ms    |

| tCPHNS<br>(Note 7)                                | CS Deselect Time (No Store)                                | 1   |              |     | μs    |

| t <sub>IW</sub> (Note 7)                          | SCL to R <sub>W</sub> Change                               |     | 100          | 500 | μs    |

| t <sub>CYC</sub>                                  | SCL Cycle Time                                             | 5   |              |     | μs    |

| t <sub>R</sub> , t <sub>F</sub> ( <u>Note 7</u> ) | SCL Input Rise and Fall Time                               |     |              | 500 | μs    |

Submit Document Feedback 6 intersil 5 Intersil 5 Intersil 6 Intersil 6 Intersil 5 Intersil 6 Inters

## Increment/Decrement Timing

### **High-Voltage Write Cycle Timing**

| SYMBOL                                    | PARAMETER                     | TYP | MAX | UNITS |

|-------------------------------------------|-------------------------------|-----|-----|-------|

| t <sub>WC</sub><br>( <u>Notes 7, 10</u> ) | Non-Volatile Write Cycle Time | 5   | 10  | ms    |

#### **XDCP Timing**

| SYMBOL                    | PARAMETER                                                                                                   | MIN | MAX | UNITS |

|---------------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| t <sub>WRL</sub> (Note 7) | SCL Rising Edge To Wiper Code Changed, Wiper Response Time After Instruction Issued (All Load Instructions) | 5   | 20  | μs    |

#### NOTES:

- 3. Absolute linearity is utilized to determine actual wiper voltage versus expected voltage =  $[V(R_{W(n)(actual)})-V(R_{W(n)(expected)})]/MI$  $V(R_{W(n)(expected)}) = n(V(R_H)-V(R_L))/255 + V(R_L)$ , with n from 0 to 255.

- 4. Relative linearity is a measure of the error in step size between taps =  $[V(R_{W(n+1)})-(V(R_{W(n)})+M])]/MI$ , with n from 0 to 254

- 5. 1 MI = Minimum Increment =  $[V(R_H)-V(R_I)]/255$

- 6. Typical values are for  $T_A = +25$ °C and nominal supply voltage.

- 7. This parameter is not 100% tested.

- 8. Ratiometric temperature coefficient =  $(V(R_W)_{T1(n)} V(R_W)_{T2(n)})/[V(R_W)_{T1(n)} (T1-T2)] \times 10^6$ , with T1 and T2 being 2 temperatures, and n from 0 to 255.

- 9. Measured with wiper at tap position 255, R<sub>L</sub> grounded, using test circuit.

- 10. t<sub>WC</sub> is the minimum cycle time to be allowed for any nonvolatile write by the user, unless Acknowledge Polling is used. It is the time from a valid STOP condition at the end of a write sequence of a 2-wire interface write operation, or from the rising edge of CS of a valid "Store" operation of the Up/Down interface, to the end of the self-timed internal nonvolatile write cycle.

- 11. The recommended power up sequence is to apply V<sub>CC</sub>/V<sub>SS</sub> first, then the potentiometer voltages. During power-up, the data sheet parameters for the DCP do not fully apply until to after VCC reaches its final value. In order to prevent unwanted tap position changes, or an inadvertant store, bring the  $\overline{CS}$  pin high before or concurrently with the  $V_{CC}$  pin on power-up.

- 12. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

Submit Document Feedback intersil FN8167.3 July 24, 2014

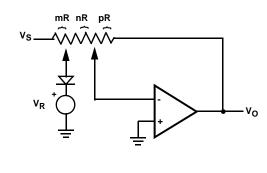

#### **Test Circuit**

## **Principles of Operation**

The X9252 is an integrated circuit incorporating four resistor arrays, their associated registers and counters, and the serial interface logic providing direct communication between the host and the digitally controlled potentiometers. This section provides detail description of the following:

- Resistor Array

- Up/Down Interface

- 2-wire Interface

#### Resistor Array Description

The X9252 is comprised of four resistor arrays. Each array contains 255 discrete resistive segments that are connected in series. The physical ends of each array are equivalent to the fixed terminals of a mechanical potentiometer ( $R_{Hi}$  and  $R_{Li}$  inputs) (see Figure 1).

At both ends of each array and between each resistor segment is a switch connected to the wiper  $(R_{Wi})$  pin.

#### **Equivalent Circuit**

Within each individual array only one switch may be turned on at a time.

These switches are controlled by a Wiper Counter Register (WCR). The 8 bits of the WCR (WCR[7:0]) are decoded to select and enable one of 256 switches (see <u>Table 1</u>). Note that each wiper has a dedicated WCR. When all bits of a WCR are zeroes, the switch closest to the corresponding  $R_{L}$  pin is selected. When all bits of a WCR are ones, the switch closest to the corresponding  $R_{H}$  pin is selected.

The WCR is volatile and may be written directly. There are four non-volatile Data Registers (DR) associated with each WCR. Each DR can be loaded into WCR. All DRs and WCRs can be read or written.

## Power-Up and Down Requirements

During power-up,  $\overline{CS}$  must be high, to avoid inadvertant "store" operations. At power-up, the contents of Data Registers DR00, DR10, DR20, and DR30, are loaded into the corresponding wiper counter register.

FIGURE 1. DETAILED BLOCK DIAGRAM OF ONE DCP

Submit Document Feedback 8 intersil 5 FN8167.3 July 24, 2014

## **Up/Down Interface Operation**

The SCL, U/ $\overline{D}$ ,  $\overline{CS}$ , DS0 and DS1 inputs control the movement of the wiper along the resistor array. With  $\overline{CS}$  set LOW the device is selected and enabled to respond to the U/ $\overline{D}$  and SCL inputs. HIGH-to-LOW transitions on SCL will increment or decrement (depending on the state of the U/ $\overline{D}$  input) a wiper counter register selected by DS0 and DS1. The output of this counter is decoded to select one of 256 wiper positions along the resistor array.

The value of the counter is stored in nonvolatile Data Registers DRi0 whenever  $\overline{CS}$  transitions HIGH while the SCL and  $\overline{WP}$  inputs are HIGH. "i" indicates the DCP number selected with pins DS1 and DS0. During a "Store" operation bits DRSel1 and DRSel0 in the Status Register must be both "0", which is their power up default value. Other combinations are reserved and must not be used.

The system may select the X9252, move the wiper, and deselect the device without having to store the latest wiper position in nonvolatile memory. After the wiper movement is performed as described above and once the new position is reached, the system must keep SCL LOW while taking  $\overline{\text{CS}}$  HIGH. The new wiper position will be maintained until changed by the system or until a power-down/up cycle recalled the previously stored data.

This procedure allows the system to always power-up to a preset value stored in nonvolatile memory; then during system operation minor adjustments could be made. The adjustments might be based on user preference, system parameter changes due to temperature drift, etc.

The state of  $U/\overline{D}$  may be changed while  $\overline{CS}$  remains LOW. This allows the host system to enable the device and then move the wiper up and down until the proper trim is attained. The 2-wire interface is disabled while  $\overline{CS}$  remains LOW.

TABLE 1. DCP SELECTION FOR UP/DOWN CONTROL

| DS1 | DS0 | SELECTED DCP |

|-----|-----|--------------|

| 0   | 0   | DCP0         |

| 0   | 1   | DCP1         |

| 1   | 0   | DCP2         |

| 1   | 1   | DCP3         |

## Mode Selection for Up/Down Control

| cs | SCL | U/D | MODE                                                                                                         |

|----|-----|-----|--------------------------------------------------------------------------------------------------------------|

| L  | ~_  | Н   | Wiper Up                                                                                                     |

| L  | ~_  | L   | Wiper Down                                                                                                   |

|    | Н   | Х   | Store Wiper Position to nonvolatile memory if WP pin is high. No store, return to standby, if WP pin is low. |

| Н  | Х   | Х   | Standby                                                                                                      |

|    | L   | Х   | No Store, Return to Standby                                                                                  |

| _  | L   | Н   | Wiper Up (not recommended)                                                                                   |

|    | L   | L   | Wiper Down (not recommended)                                                                                 |

#### 2-Wire Serial Interface

#### **Protocol Overview**

The device supports a bidirectional bus oriented protocol. The protocol defines any device that sends data onto the bus as a transmitter, and the receiving device as the receiver. The device controlling the transfer is called the master and the device being controlled is called the slave. The master always initiates data transfers, and provides the clock for both transmit and receive operations. The X9252 operates as a slave in all applications.

All 2-wire interface operations must begin with a START, followed by a Slave Address byte. The Slave Address selects the X9252, and specifies if a Read or Write operation is to be performed.

All Communication over the 2-wire interface is conducted by sending the MSB of each byte of data first.

# Serial Clock and Data

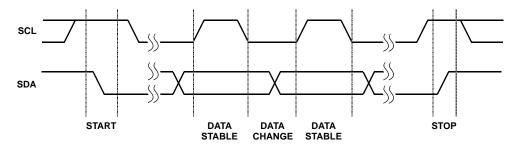

Data states on the SDA line can change only while SCL is LOW. The SDA state changes while SCL is HIGH are reserved for indicating START and STOP conditions (see <u>Figure 2</u>). On power-up of the X9252, the SDA pin is in the input mode.

#### Serial Start Condition

All commands are preceded by the START condition, which is a HIGH-to-LOW transition of SDA while SCL is HIGH. The device continuously monitors the SDA and SCL lines for the START condition and does not respond to any command until this condition has been met (see Figure 2).

#### Serial Stop Condition

All communications must be terminated by a STOP condition, which is a LOW-to-HIGH transition of SDA while SCL is HIGH. The STOP condition is also used to place the device into the Standby power mode after a read sequence. A STOP condition can only be issued after the transmitting device has released the bus (see Figure 2).

Submit Document Feedback 9 intersil 5 FN8167.3 July 24, 2014

FIGURE 2. VALID DATA CHANGES, START, AND STOP CONDITIONS

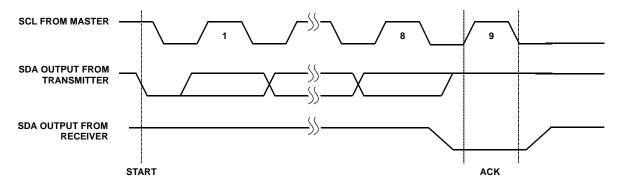

FIGURE 3. ACKNOWLEDGE RESPONSE FROM RECEIVER

#### Serial Acknowledge

An ACK (Acknowledge), is a software convention used to indicate a successful data transfer. The transmitting device, either master or slave, releases the bus after transmitting eight bits. During the ninth clock cycle, the receiver pulls the SDA line LOW to acknowledge the reception of the eight bits of data (see Figure 3).

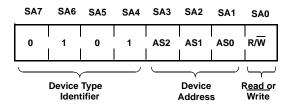

The device responds with an ACK after recognition of a START condition followed by a valid Slave Address byte. A valid Slave Address byte must contain the Device Type Identifier 0101, and the Device Address bits matching the logic state of pins A2, A1, and A0 (see Figure 4).

If a write operation is selected, the device responds with an ACK after the receipt of each subsequent eight-bit word.

In the read mode, the device transmits eight bits of data, releases the SDA line, and then monitors the line for an ACK. The device continues transmitting data if an ACK is detected. The device terminates further data transmissions if an ACK is not detected. The master must then issue a STOP condition to place the device into a known state.

#### Slave Address Byte

Following a START condition, the master must output a Slave Address Byte (Figure 4). This byte includes three parts:

- The four MSBs (SA7-SA4) are the Device Type Identifier, which must always be set to 0101 in order to select the X9252.

- The next three bits (SA3-SA1) are the Device Address bits (AS2-AS0). To access any part of the X9252's memory, the value of bits AS2, AS1, and AS0 must correspond to the logic levels at pins A2, A1, and A0 respectively.

- The LSB (SA0) is the R/W bit. This bit defines the operation to be performed on the device being addressed. When the R/W bit is "1", then a Read operation is selected. A "0" selects a Write operation.

| SLAVE ADDRESS<br>BIT(S) | DESCRIPTION                    |

|-------------------------|--------------------------------|

| SA7-SA4                 | Device Type Identifier         |

| SA3-SA1                 | Device Address                 |

| SA0                     | Read or Write Operation Select |

FIGURE 4. SLAVE ADDRESS (SA) FORMAT

Submit Document Feedback 10 intersil\* FN8167.3

July 24, 2014

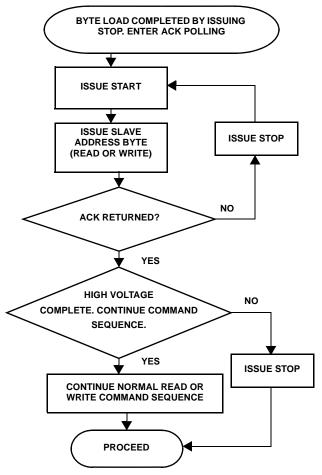

#### Nonvolatile Write Acknowledge Polling

After a nonvolatile write command sequence is correctly issued (including the final STOP condition), the X9252 initiates an internal high voltage write cycle. This cycle typically requires 5ms. During this time, any Read or Write command is ignored by the X9252. Write Acknowledge Polling is used to determine whether a high voltage write cycle is completed.

During acknowledge polling, the master first issues a START condition followed by a Slave Address Byte. The Slave Address Byte contains the X9252's Device Type Identifier and Device Address. The LSB of the Slave Address (R/W) can be set to either 1 or 0 in this case. If the device is busy within the high voltage cycle, then no ACK is returned. If the high voltage cycle is completed, an ACK is returned and the master can then proceed with a new Read or Write operation (see Figure 5).

FIGURE 5. ACKNOWLEDGE POLLING SEQUENCE

## 2-Wire Serial Interface Operation

#### X9252 Digital Potentiometer Register Organization

Refer to the "Functional Diagram" on page 2. There are four Digitally Controlled Potentiometers, referred to as DCPi, i = 0, 1, 2, 3. Each potentiometer has one volatile Wiper Control Register (WCR) with the corresponding number, WCRi, i = 0, 1, 2, 3. Each potentiometer also has four nonvolatile registers to store wiper position or general data, these are numbered DRi0, DRi1, DRi2 and DRi3, i = 0, 1, 2, 3.

The registers are organized in five pages of four, with one page consisting of the WCRi (i = 0 to 3), a second page containing the DRi0 (i = 0 to 3), a third page containing the DRi1, and so forth. These pages can be written to four bytes at time. In this manner all four potentiometer WCRs can be updated in a single serial write (see "Page Write Operation" on page 14), as well as all four registers of a given page in the DR array.

The unique feature of the X9252 device is that writing or reading to a Data Register of a given DCP automatically updates/moves the WCR of that DCP with the content of the DR. In this manner data can be moved from a particular DCP register to that DCP's WCR just by performing a 2-wire read operation. Simultaneously, that data byte can be utilized by the host.

#### Status Register Organization

The Status Register (SR) is used in read and write operations to select the appropriate DCP register. Before any DCP register can be accessed, the SR must be set to the correct value. It is accessed by setting the Address Byte to 07h (see Table 3). Do this by Writing the Slave Address followed by a Byte Address of 07h. The SR is volatile and defaults to 00h on power-up. It is an 8-bit register containing three control bits in the 3 LSBs as follows:

| 7 | 6 | 5      | 4  | 3 | 2      | 1      | 0        |

|---|---|--------|----|---|--------|--------|----------|

|   | R | eserve | ed |   | DRSel1 | DRSel0 | NVEnable |

Bits DRSel1 and DRSel0 determine which Data Register of a DCP is selected for a given operation. NVEnable is used to select the volatile WCR if "0", and one of the nonvolatile DCP registers if "1". Table 2 shows this register organization. "Store" operations using the Up/Down interface require that bits DRSel1 and DRSel0 are set to "0".

Submit Document Feedback intersil FN8167.3 11

**TABLE 2. REGISTER NUMBERING**

| ,        | STATUS REG (No | ote 13) (Addr: 07H | )                 | REGISTERED SELECTED (Note 14) |             |             |             |  |

|----------|----------------|--------------------|-------------------|-------------------------------|-------------|-------------|-------------|--|

| RESERVED | DRSel1         | DRSel0<br>BIT-1    | NVEnable<br>BIT-0 | DCP0                          | DCP1        | DCP2        | DCP3        |  |

| BITS 7-3 | BIT-2          |                    |                   | (ADDR: 00h)                   | (ADDR: 01h) | (ADDR: 02h) | (ADDR: 03h) |  |

| Reserved | Х              | Х                  | 0                 | WCR0                          | WCR1        | WCR2        | WCR3        |  |

|          | 0              | 0                  | 1                 | DR00                          | DR10        | DR20        | DR30        |  |

|          | 0              | 1                  | 1                 | DR01                          | DR11        | DR21        | DR31        |  |

|          | 1              | 0                  | 1                 | DR02                          | DR12        | DR22        | DR32        |  |

|          | 1              | 1                  | 1                 | DR03                          | DR13        | DR23        | DR33        |  |

#### To read or write the contents of a single Data Register or Wiper Register:

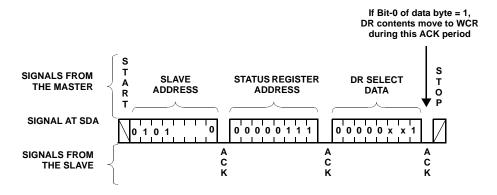

13. Load the status register (using a write command) to select the row (see Figure 6)

Writing a 1, 3, 5, or 7 to the Status Register specifies that the subsequent read or write command will access a Data Register. This status register operation also initiates a transfer of the contents of the selected data register to its associated WCR for all DCPs. So, for example, writing '03h' to the status register causes the value in DR01 to move to WCR0, DR11 to move to WCR1, DR21 to move to WCR2, and DR31 to move to WCR3.

Writing a 0 to bit '0' of the status register specifies that the subsequent read or write command will access a wiper counter register. Each WCR can be written to individually, without affecting the contents of any other.

14. Access the desired DR or WCR using a new write or read command (see Figure 7 for write and Figure 9 for read.)

Specify the desired column (DCP number) by sending the DCP address as part of this read or write command.

FIGURE 6. STATUS REGISTER WRITE (USES STANDARD BYTE WRITE SEQUENCE TO SET UP ACCESS TO A DATA REGISTER)

Submit Document Feedback 12 intersil 5 FN8167.3 July 24, 2014

START

#### DCP Addressing for 2-Wire Interface

Once the register number has been selected by a 2-wire instruction, then the DCP number is determined by the Address Byte of the following instruction. Note again that this enables a complete page write of the DRs of all four potentiometers at once. The register addresses accessible in the X9252 include:

TABLE 3. 2-WIRE INTERFACE ADDRESS BYTE

| ADDRESS (HEX) | CONTENTS        |

|---------------|-----------------|

| 0             | DCP 0           |

| 1             | DCP 1           |

| 2             | DCP 2           |

| 3             | DCP 3           |

| 4             | Not Used        |

| 5             | Not Used        |

| 6             | Not Used        |

| 7             | Status Register |

All other address bits in the Address Byte must be set to "0" during 2-wire write operations and their value should be ignored when read.

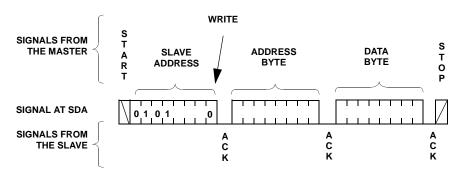

#### Byte Write Operation

For any Byte Write operation, the X9252 requires the Slave Address byte, an Address Byte, and a Data Byte (see Figure 7). After each of them, the X9252 responds with an ACK. The master then terminates the transfer by generating a STOP condition. At this time, if the write operation is to a volatile register (WCR, or SR), the X9252 is ready for the next read or write operation. If the write operation is to a nonvolatile register (DR), and the  $\overline{\text{WP}}$  pin is high, the X9252 begins the internal write cycle to the nonvolatile memory. During the internal nonvolatile write cycle, the X9252 does not respond to any requests from the master. The SDA output is at high impedance.

The SR bits and  $\overline{\text{WP}}$  pin determine the register being accessed through the 2-wire interface (see Table 2).

As noted before, any write operation to a Data Register (DR), also transfers the contents of all the data registers in that row to their corresponding WCR.

For example, to write 3Ahex to the Data Register 1 of DCP2 the following sequence is required:

| 0171111                                                                    |              |                                               |  |  |  |  |

|----------------------------------------------------------------------------|--------------|-----------------------------------------------|--|--|--|--|

| Slave Address<br>ACK                                                       | 0101 0000    | (Hardware Address = 000, and a Write Command) |  |  |  |  |

| Address Byte<br>ACK                                                        | 0000 0111    | (Indicates Status Register Address)           |  |  |  |  |

| Data Byte<br>ACK                                                           | 0000 0011    | (Data Register 1 and NVEnable Selected)       |  |  |  |  |

| Note: at this ACK, the WCRs are all updated with their respective DR. STOP |              |                                               |  |  |  |  |

| START                                                                      | 0.4.0.4.0000 |                                               |  |  |  |  |

Slave Address

0101 0000

(Hardware Address = 000, Write Command)

ACK

Address Byte

0000 0010

(Access DCP2)

ACK

Data Byte

0011 1010

(Write Data Byte 3Ah)

ACK

STOP

During the sequence of this example,  $\overline{WP}$  pin must be high, and A0, A1, and A2 pins must be low. When completed, the DR21 register and the WCR2 will be set to 3Ah and the other Data Register in Row 1 will transfer their other contents to the respective WCR's

FIGURE 7. BYTE WRITE SEQUENCE

Submit Document Feedback 13 intersil FN8167.3

July 24, 2014

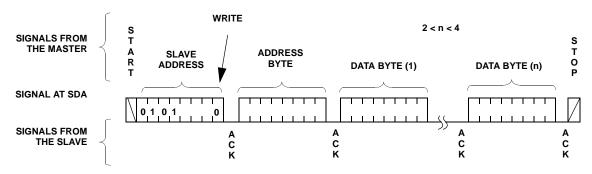

#### Page Write Operation

As stated previously, the memory is organized as a single Status Register (SR), and four pages of four registers each. Each page contains one Data Register for each DCP. The order of the bytes within a page is DR0i, followed by DR1i, followed by DR2i, and then DR3i, with i being the Data Register number (0, 1, 2, or 3). Normally a page write operation will be used to efficiently update all four data registers and WCR in a single write command, starting at DCP0 and finishing with DCP3.

In order to perform a Page Write operation to the memory array, the NVEnable bit in the SR must first be set to "1".

A Page Write operation is initiated in the same manner as the byte write operation; but instead of terminating the write cycle after the first data byte is transferred, the master can transmit up to 4 bytes (see Figure 8). After the receipt of each byte, the X9252 responds with an ACK, and the internal DCP address counter is incremented by one. The page address remains constant. When the counter reaches

the end of the page (DR3i, 03hex), it "rolls over" and goes back to the first byte of the same page (DR0i, 00hex).

For example, if the master writes 3 bytes to a page starting at location DR22, the first 2 bytes are written to locations DR22 and DR32, while the last byte is written to locations DR02. Afterwards, the DCP counter would point to location DR12. If the master supplies more than 4 bytes of data, then new data overwrites the previous data, one byte at a time.

The master terminates the loading of Data Bytes by issuing a STOP condition, which initiates the nonvolatile write cycle. As with the Byte Write operation, all inputs are disabled until completion of the internal write cycle. If the WP pin is low, the nonvolatile write cycle doesn't start and the bytes are discarded.

Notice that the Data Bytes are also written to the WCR of the corresponding DCPs, therefore in the above example, WCR2, WCR3, and WCR0 are also written and WCR1 is updated with the contents of DR12.

FIGURE 8. PAGE WRITE OPERATION

Submit Document Feedback 14 intersil\* FN8167.3

July 24, 2014

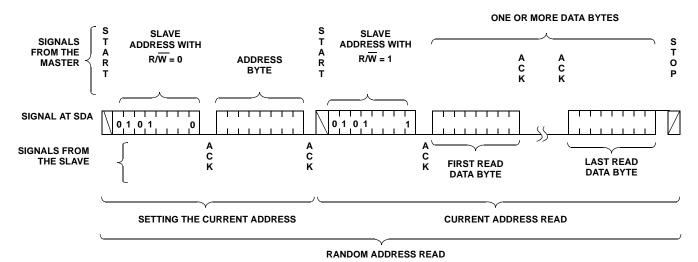

#### Move/Read Operation

The Move/Read operation simultaneously reads the contents of a Data Register (DR) and moves the contents into the corresponding DCP's WCR and the WCRs of all DCPs are updated with the content of their corresponding DR. Move/Read operation consists of a one byte, or three byte instruction followed by one or more Data Bytes (see Figure 9). To read an arbitrary byte, the master initiates the operation issuing the following sequence: a START, the Slave Address byte with the  $R/\overline{W}$  bit set to "0", an Address Byte, a second START, and a second Slave Address byte with the  $R/\overline{W}$  bit set to "1". After each of the three bytes, the X9252 responds with an ACK. Then the X9252 transmits

Data Bytes as long as the master responds with an ACK during the SCL cycle following the eight bit of each byte. The master terminates the Move/Read operation (issuing a STOP condition) following the last bit of the last Data Byte.

The first byte being read is determined by the current DCP address and by the Status Register bits, according to Table 2. If more than one byte is read, the DCP address is incremented by one after each byte, in the same way as during a Page Write operation. After reaching DCP3, the DCP address "rolls over" to DCP0.

On power-up, the Address pointer is set to the Data Register 0 of DCP0.

FIGURE 9. MOVE/READ SEQUENCE

Submit Document Feedback 15 intersil FN8167.3

July 24, 2014

# **Applications Information**

# **Basic Configurations of Electronic Potentiometers**

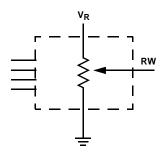

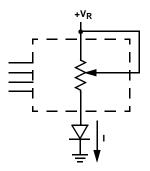

FIGURE 10. THREE TERMINAL POTENTIOMETER; VARIABLE **VOLTAGE DIVIDER**

FIGURE 11. TWO TERMINAL VARIABLE RESISTOR; **VARIABLE CURRENT**

# **Application Circuits**

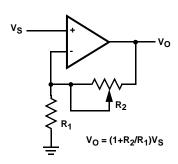

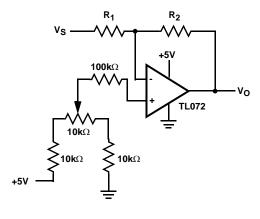

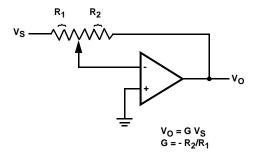

FIGURE 12. NONINVERTING AMPLIFIER

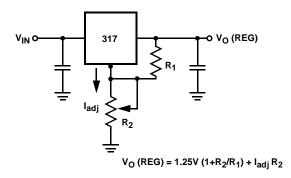

FIGURE 13. VOLTAGE REGULATOR

FIGURE 14. OFFSET VOLTAGE ADJUSTMENT

$\begin{aligned} &V_{UL} = \{R_1/(R_1 + R_2)\} \ V_O(max) \\ &RL_L = \{R_1/(R_1 + R_2)\} \ V_O(min) \end{aligned}$

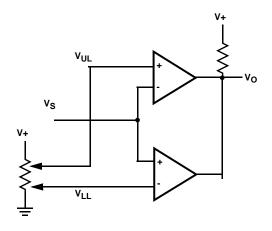

FIGURE 15. COMPARATOR WITH HYSTERISIS

Submit Document Feedback

intersil<sup>®</sup>

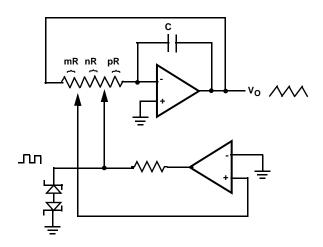

# Application Circuits (Continued)

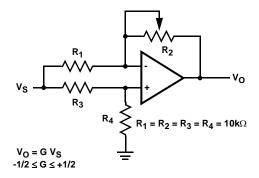

FIGURE 16. ATTENUATOR

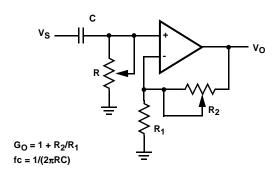

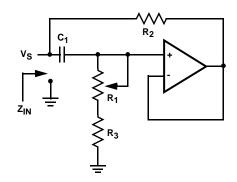

FIGURE 17. FILTER

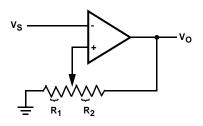

FIGURE 18. INVERTING AMPLIFIER

$Z_{IN} = R_2 + s R_2 (R_1 + R_3) C_1 = R_2 + s Leq$  $(R_1 + R_3) >> R_2$

FIGURE 19. EQUIVALENT L-R CIRCUIT

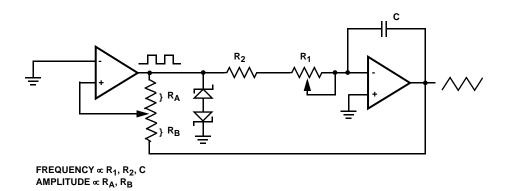

FIGURE 20. FUNCTION GENERATOR

# **Application Circuits** (Continued)

FIGURE 21. WINDOW COMPARATOR

FIGURE 22. SHUNT LIMITER

FIGURE 23. FUNCTION GENERATOR

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9001 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

Submit Document Feedback 18 intersil FN8

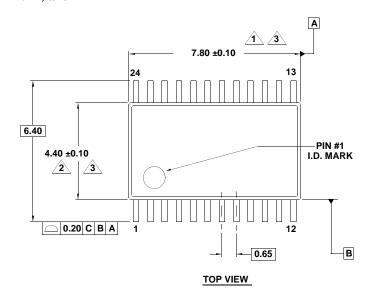

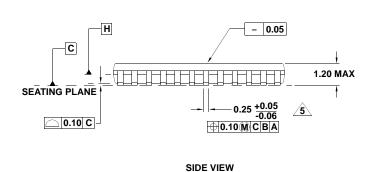

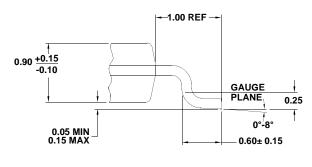

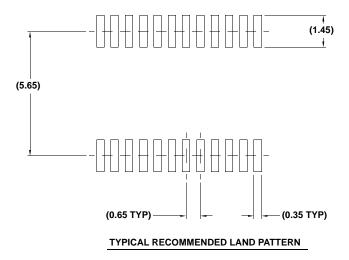

# **Package Outline Drawing**

M24.173 24 LEAD THIN SHRINK SMALL OUTLINE PACKAGE (TSSOP) Rev 1, 5/10

#### NOTES:

1. Dimension does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15 per side.

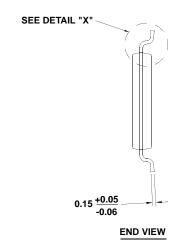

DETAIL "X"

- 2. Dimension does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.25 per side.

- 3. Dimensions are measured at datum plane H.

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 5. Dimension does not include dambar protrusion. Allowable protrusion shall be 0.08mm total in excess of dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm.

- 6. Dimension in ( ) are for reference only.

- 7. Conforms to JEDEC MO-153.

intersil Submit Document Feedback 19 FN8167.3