1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

## **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

Pb-Free and RoHS Compliant

# HI1171

#### October 26, 2005

### 8-Bit, 40 MSPS, High Speed D/A Converter

#### Features

- Throughput Rate ..... 40MHz

- Resolution ...... 8-Bit

- Integral Linearity Error ..... 0.25 LSB

- Low Glitch Noise

- Low Power Consumption (Max) .....80mW

- Evaluation Board Available (HI1171-EV)

- Direct Replacement for the Sony CXD1171

#### Applications

- Wireless Telecommunications

- Signal Reconstruction

- Direct Digital Synthesis

- Imaging

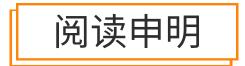

Pinout

- Presentation and Broadcast Video

- Graphics Displays

- Signal Generators

#### Description

The HI1171 is an 8-bit, 40MHz, high speed D/A converter. The converter incorporates an 8-bit input data register with blanking capability, and current outputs. The HI1171 features low glitch outputs. The architecture is a current cell arrangement to provide low linearity errors.

The HI1171 is available in an Industrial temperature range and is offered in a 24 lead (200 mil) SOIC plastic package. For dual version, please refer to the HI1177 Data Sheet. For triple version, please refer to the HI1178 Data Sheet.

#### Ordering Information

| PART<br>NUMBER | TEMP. RANGE<br>( <sup>o</sup> C) | PACKAGE         | PKG. NO. |

|----------------|----------------------------------|-----------------|----------|

| HI1171JCB      | -40 to 85                        | 24 Ld SOIC      | M24.2-S  |

| HI1171-EV      | 25                               | Evaluation Boar | d        |

#### **Absolute Maximum Ratings**

| Digital Supply Voltage DV <sub>DD</sub> to DV <sub>SS</sub> +7.0V |

|-------------------------------------------------------------------|

| Analog Supply Voltage AV <sub>DD</sub> to AV <sub>SS</sub> +7.0V  |

| Input Voltage V <sub>DD</sub> to V <sub>SS</sub> V                |

| Output Current                                                    |

| Operating Conditions                                              |

Temperature Range ......-40°C to 85°C

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)          | θ <sub>JA</sub> ( <sup>o</sup> C/W)     |

|-----------------------------------------------|-----------------------------------------|

| SOIC Package                                  | 98                                      |

| Maximum Junction Temperature, Plastic Package | 150 <sup>0</sup> C                      |

| Maximum Storage Temperature Range             | 65 <sup>0</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering 10s)      | 300 <sup>0</sup> C                      |

| (SOIC - Lead Tips Only)                       |                                         |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\text{JA}}$  is measured with the component mounted on an evaluation PC board in free air.

#### Electrical Specifications

$AV_{DD}$  = +4.75V to +5.25V,  $DV_{DD}$  = +4.75 to +5.25V,  $V_{REF}$  = +2.0V,  $f_S$  = 40MHz, CLK Pulse Width = 12.5ns,  $T_A$  = 25°C (Note 4)

| PARAMETER                                              | TEST CONDITIONS                    | MIN  | TYP | МАХ   | UNITS  |

|--------------------------------------------------------|------------------------------------|------|-----|-------|--------|

| SYSTEM PERFORMANCE                                     |                                    |      |     |       |        |

| Resolution, n                                          |                                    | -    | 8   | -     | Bits   |

| Integral Linearity Error, INL                          | f <sub>S</sub> = 40MHz (End Point) | -0.5 | -   | 1.3   | LSB    |

| Differential Linearity Error, DNL                      | f <sub>S</sub> = 40MHz             | -    | -   | ±0.25 | LSB    |

| Offset Error, V <sub>OS</sub>                          | (Note 2)                           | -    | -   | 1     | mV     |

| Full Scale Error, FSE (Adjustable to Zero)             | (Note 2)                           | -    | -   | ±13   | LSB    |

| Full Scale Output Current, I <sub>FS</sub>             |                                    | -    | 10  | 15    | mA     |

| Full Scale Output Voltage, V <sub>FS</sub>             |                                    | 1.9  | 2.0 | 2.1   | V      |

| Output Voltage Range, V <sub>FSR</sub>                 |                                    | 0.5  | 2.0 | 2.1   | V      |

| DYNAMIC CHARACTERISTICS                                |                                    |      |     | •     |        |

| Throughput Rate                                        | See Figure 7                       | 40.0 | -   | -     | MHz    |

| Glitch Energy, GE                                      | R <sub>OUT</sub> = 75Ω             | -    | 30  | -     | pV-s   |

| Differential Gain, $\Delta A_V$ (Note 3)               |                                    | -    | 1.2 | -     | %      |

| Differential Phase, ∆                                  |                                    | -    | 0.5 | -     | Degree |

| REFERENCE INPUT                                        |                                    |      |     | •     |        |

| Voltage Reference Input Range                          |                                    | 0.5  | -   | 2.0   | V      |

| Reference Input Resistance                             | (Note 3)                           | 1.0  | -   | -     | MΩ     |

| DIGITAL INPUTS                                         |                                    |      |     |       |        |

| Input Logic High Voltage, V <sub>IH</sub>              | (Note 3)                           | 3.0  | -   | -     | V      |

| Input Logic Low Voltage, V <sub>IL</sub>               | (Note 3)                           | -    | -   | 1.5   | V      |

| Input Logic Current, I <sub>IL</sub> , I <sub>IH</sub> | (Note 3)                           | -    | -   | ±5.0  | μΑ     |

| Digital Input Capacitance, C <sub>IN</sub>             | (Note 3)                           | -    | 5.0 | -     | pF     |

| TIMING CHARACTERISTICS                                 |                                    | •    | -   | -     | -      |

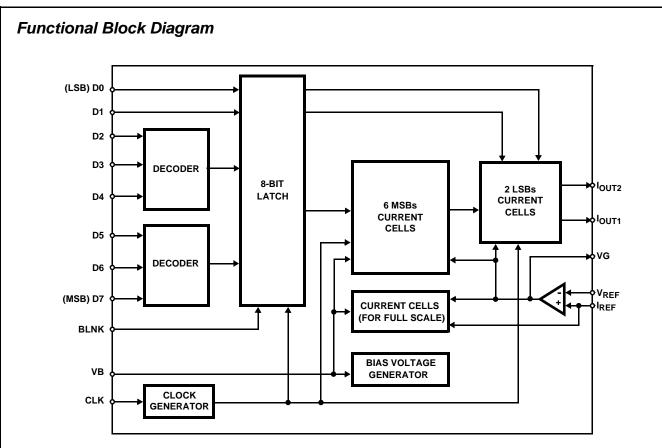

| Data Setup Time, t <sub>SU</sub>                       | See Figure 1                       | 5    | -   | -     | ns     |

| Data Hold Time, t <sub>HLD</sub>                       | See Figure 1                       | 10   | -   | -     | ns     |

#### HI1171

#### **Electrical Specifications**

$AV_{DD}$  = +4.75V to +5.25V,  $DV_{DD}$  = +4.75 to +5.25V,  $V_{REF}$  = +2.0V,  $f_S$  = 40MHz, CLK Pulse Width = 12.5ns,  $T_A$  = 25 $^o$ C (Note 4) **(Continued)**

| PARAMETER                                                            | TEST CONDITIONS                       | MIN  | ТҮР  | MAX  | UNITS |

|----------------------------------------------------------------------|---------------------------------------|------|------|------|-------|

| Propagation Delay Time, t <sub>PD</sub>                              | See Figure 9                          | -    | 10   | -    | ns    |

| Settling Time, t <sub>SET</sub> (to <sup>1</sup> / <sub>2</sub> LSB) | See Figure 1                          | -    | 10   | 15   | ns    |

| CLK Pulse Width, t <sub>PW1</sub> , t <sub>PW2</sub>                 | See Figure 1                          | 12.5 | -    | -    | ns    |

| POWER SUPPLY CHARACTERISITICS                                        |                                       |      |      |      |       |

| IAV <sub>DD</sub>                                                    | 14.3MHz, at Color Bar Data Input      | -    | 10.9 | 11.5 | mA    |

| IDV <sub>DD</sub>                                                    | 14.3MHz, at Color Bar Data Input      | -    | 4.2  | 4.8  | mA    |

| Power Dissipation                                                    | $200\Omega$ load at $2V_{P-P}$ Output | -    | -    | 80   | mW    |

NOTES:

2. Excludes error due to external reference drift.

3. Parameter guaranteed by design or characterization and not production tested.

4. Electrical specifications guaranteed only under the stated operating conditions.

FIGURE 1.

| 24 PIN<br>SOIC | PIN<br>NAME             | PIN DESCRIPTION                                                                                                                                                                  |

|----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-8            | D0(LSB) thru<br>D7(MSB) | Digital Data Bit 0, the Least Significant Bit thru Digital Data Bit 7, the Most Significant Bit.                                                                                 |

| 9              | BLNK                    | Blanking Line, used to clear the internal data register to the zero condition when High, normal operation when Low.                                                              |

| 10, 13         | DV <sub>SS</sub>        | Digital Ground.                                                                                                                                                                  |

| 11             | VB                      | Voltage Bias, connect a $0.1\mu$ F capacitor to DV <sub>SS</sub> .                                                                                                               |

| 12             | CLK                     | Data Clock Pin 100kHz to 40MHz.                                                                                                                                                  |

| 14             | AV <sub>SS</sub>        | Analog Ground.                                                                                                                                                                   |

| 15             | I <sub>REF</sub>        | Current Reference, used to set the current range. Connect a resistor to $AV_{SS}$ that is 16 times greater than the resistor on $I_{OUT1}$ . (See Typical Applications Circuit). |

| 16             | V <sub>REF</sub>        | Input Reference Voltage used to set the output full scale range.                                                                                                                 |

| 24 PIN<br>SOIC | PIN<br>NAME       | PIN DESCRIPTION                                                                                  |

|----------------|-------------------|--------------------------------------------------------------------------------------------------|

| 17             | VG                | Voltage Ground, connect a $0.1\mu F$ capacitor to AV <sub>DD</sub> .                             |

| 18, 19, 22     | AV <sub>DD</sub>  | Analog Supply 4.75V to 7V.                                                                       |

| 20             | I <sub>OUT1</sub> | Current Output Pin.                                                                              |

| 21             | I <sub>OUT2</sub> | Current Output pin used for a virtual ground connection. Usually connected to AV <sub>SS</sub> . |

| 23, 24         | DV <sub>DD</sub>  | Digital Supply 4.75V to 7V.                                                                      |

#### **Detailed Description**

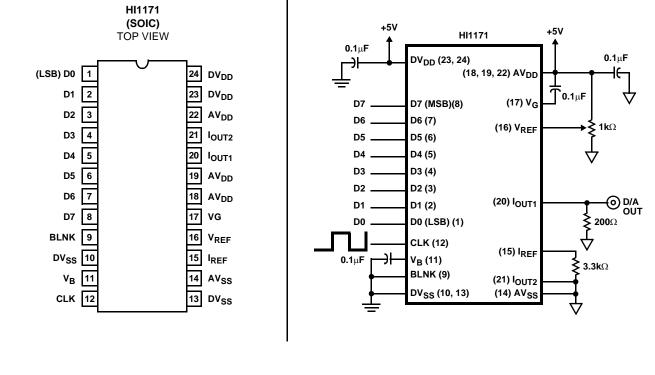

The HI1171 is an 8-bit, current out D/A converter. The DAC can convert at 40MHz and run on a single +5V supply. The architecture is an encoded, switched current cell arrangement.

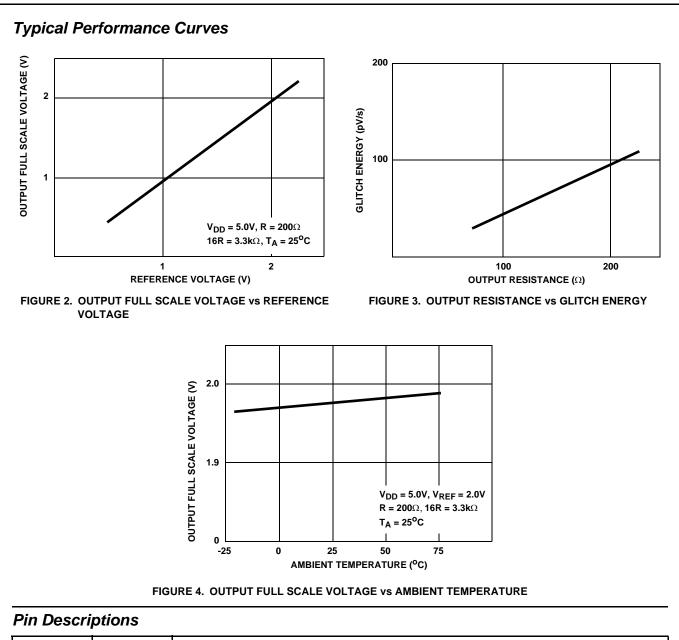

#### Voltage Output Mode

The output current of the HI1171 can be converted into a voltage by connecting an external resistor to IOUT1. To calculate the output resistor use the following equation:

$R_{OUT} = V_{FS} / I_{FS}$ ,

where  $V_{\text{FS}}$  can range from +0.5V to +2.0V and  $I_{\text{FS}}$  can range from 0mA to 15mA.

In setting the output current the IREF pin should have a resistor connected to it that is 16 times greater than the output resistor:

#### R<sub>RFF</sub> = 16 x R<sub>OUT</sub>

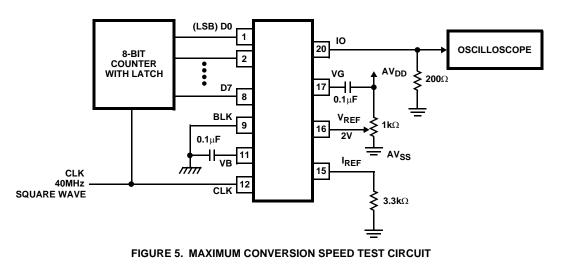

#### **Test Circuits**

As the values of both R<sub>OUT</sub> and R<sub>REF</sub> increase, power consumption is decreased, but glitch energy and output settling time is increased.

#### **Clock Phase Relationship**

The internal latch is closed when the clock line is high. The latch can be cleared by the BLNK line. When BLNK is set (HIGH) the contents of the internal data latch will be cleared. When BLNK is low data is updated by the CLK.

#### **Noise Reduction**

To reduce power supply noise separate analog and digital power supplies should be used with 0.1µF ceramic capacitors placed as close to the body of the HI1171 as possible. The analog (AV<sub>SS</sub>) and digital (DV<sub>SS</sub>) ground returns should be connected together back at the power supply to ensure proper operation from power up.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time withou notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com