1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

#### FEATURES

- TI AM1810 ARM9 Application Processor

- 375 MHz ARM926EJ-S MPU

- 16 KB L1 Program Cache

- 16 KB L1 Data Cache

- 8 KB Internal RAM

- 64 KB boot ROM

- JTAG Emulation/Debug

- On-Board Xilinx Spartan-6 FPGA

- Up To XC6SLX45

- Up To 2,088 KBits Block RAM

- Up To 6,822 Slices (6 Input LUTs)

- 1050 Mbps data rate

- JTAG Interface/Debug

- Up To 256 MB mDDR2 CPU RAM

- Up To 512 MB Parallel NAND FLASH

- 8 MB SPI based NOR FLASH

- Integrated Power Management

- Standard SO-DIMM-200 Interface

- 96 FPGA User I/O Pins

- 10/100 EMAC MII / MDIO

- 2 UARTS

- 2 McBSPs

- 2 USB Ports

- Video Output

- Camera/Video Input

- MMC/SD

- SATA

- ePWM, eCAP

- EMIFA

- Single 3.3V Power Supply

- PROFIBUS Interface

- Certified by PI International

- Real-Time Linux Drivers

- Up to 6Mbaud operation

#

#### APPLICATIONS

- Embedded Instrumentation

- Industrial Automation

- Industrial Instrumentation

- Medical Instrumentation

- Embedded Control Processing

- Network Enabled Data Acquisition

- Test and Measurement

- Software Defined Radio

- Bar Code Scanners

- Power Protection Systems

- Portable Data Terminals

#### BENEFITS

- Rapid Development / Deployment

- Multiple Connectivity and Interface Options

- Rich User Interfaces

- High System Integration

- High Level OS Support

- High Level OS Support

- Linux

- QNX

- Windows Embedded CE Ready

- ThreadX Real Time OS

#### DESCRIPTION

The MitySOM-1810F is a highly configurable, very small form-factor processor card that features a Texas Instruments AM1810 375MHz ARM Applications Processor tightly integrated with the Xilinx Spartan-6 Field Programmable Gate Array (FPGA), PROFIBUS, FLASH (NAND and NOR) and mDDR2 RAM memory subsystems.

The design of the MitySOM-1810F allows end users the capability to develop programs/logic images for both the ARM processor and the FGPA. The MitySOM-1810F provides a complete and flexible digital processing infrastructure necessary for the most demanding embedded applications development.

The AM1810 includes an ARM926EJ-S micro-processor unit (MPU) capable of running the rich software applications programming interfaces (APIs) expected by modern system designers. The ARM architecture supports several operating systems, including Real-Time Linux, QNX and Windows XP embedded. Linux drivers are available for all interfaces, including the PROFIBUS interface.

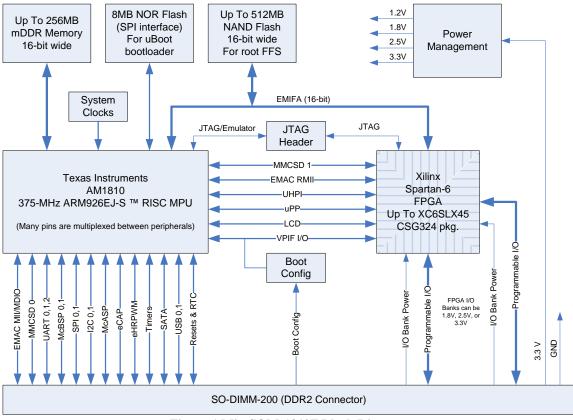

Figure 1 MitySOM-1810F Block Diagram

Figure 1 provides a top level block diagram of the MitySOM-1810F processor card. As shown in the figure, the primary interface to the MitySOM-1810F is through a standard SO-DIMM-200 card edge interface. The interface provides power, synchronous serial connectivity, and up to 96 pins of configurable FPGA I/O for application defined interfacing. Details of the SO-DIMM-200 connector interface are included in the SO-DIMM-200 Interface Description, below.

#### **PROFIBUS Interface**

Texas Instruments Inc. (TI) has integrated PROFIBUS functionality into its AM1810 Sitara ARM microprocessor (MPU). The solution utilizes one of the onboard UARTS and connects directly to the RS-485 transceiver and therefore eliminates the need of an external PROFIBUS ASIC or FPGA. Customers using the MitySOM-1810 in their industrial application can save cost and reduce design complexity as well as PCB space. Furthermore, the industrial application benefits from the low-power architecture of the Sitara ARM MPU and the MitySOM-1810 platform from TI and Critical Link.

The AM1810 Sitara ARM MPU PROFIBUS Slave solution has been certified by PROFIBUS International (PI).

The PROFIBUS real-time frame handler (Fieldbus Data Link or FDL) is encapsulated in the Programmable Real-Time Unit Subsystem (PRUSS), which is part of the AM1810 Sitara ARM MPU on-chip peripherals. The PRUSS uses one Universal Asynchronous Receiver/Transmitter (UART) and a timer to generate PROFIBUS-compliant frames. The industrial application and the PROFIBUS DP-Protocol (Layer 7) are operated on the ARM. The solution can be completed with an RS-485 transceiver suitable for harsh environments, such as TI's ISO1176T or ISO1176 placed on the base board to the MitySOM-1810F.

The PROFIBUS subsystem uses the PRUs that implement real-time frame handling; PROFIBUS message transmission, frame validation and communication with the ARM processor. The PROFIBUS subsystem interfaces with one of the UARTs in the AM1810 Sitara ARM MPU, which is designated for PROFIBUS communication at up to 6Mbaud data rate. The PRU uses interrupts to interact with the ARM where the PROFIBUS stack (Layer 7, DP Protocol) and the industrial application is run. All process data handling like cyclic, acyclic and service access point (SAP) between the PROFIBUS stack on ARM and the PRU is through the internal memory.

Additional details about the AM1810 Sitara ARM MPU, available peripherals and their features are provided in the data sheet at the TI website (www.ti.com/am1810).

# FPGA Bank I/O

The MitySOM-1810F provides 96 lines of FPGA I/O directly to the SO-DIMM-200 card edge interface. The 96 lines of FPGA I/O are distributed across 2 banks of the FPGA. These I/O lines and their associated logic are completely configurable within the FPGA at the end user's discretion.

With the Xilinx Spartan-6 series FPGA, up to the XC6SLX45, each of the user controlled banks may be configured to operate on a different electrical interface standard based on input voltage provided at the card edge connector. The banks support 3.3V, 2.5V, and 1.8V standard CMOS switching level technology. In addition, the I/O lines from the FPGA have been routed as differential pairs and support higher speed LVDS standards as well as SSTL 2.5 switching standards. Various forms of termination (pull-up/pull-down,

digitally controlled impedance matching) are available within the FPGA switch fabric. Refer to the Xilinx Spartan 6 user's guide for more information.

#### AM1810 mDDR2 Memory Interface

The AM1810 includes a dedicated DDR2 SDRAM memory interface. The MitySOM-1810F includes up to 256 MB of mDDR2 RAM integrated with the AM1810 processor. The bus interface is capable of burst transfer rates of 532 MB / second.

#### AM1810 SPI NOR FLASH Interface

The MitySOM-1810F includes 8 MB of SPI NOR FLASH. This FLASH memory is intended to store a factory provided bootloader, and typically a compressed image of a Linux kernel for the ARM core processor.

# EMIFA / NAND FLASH Interface

The Asynchronous External Memory Interface (EMIFA) interface available on the AM1810 is available on the SO-DIMM-200 connector. The EMIFA interface includes 3 chip select spaces. The EMIF interface supports multiple data width transfers and bus wait state configurations based on chip select space. 8, and 16 bit data word sizes may be used.

Up to 512 MB of on-board NAND FLASH memory is connected to the AM1810 using the EMIFA bus. The FLASH memory is 8 bits wide and is connected to the third chip select line of the EMIFA (CE1). The FLASH memory is typically used to store the following types of data:

- ARM Linux / Windows Embedded CE / QNX embedded root file-system

- FPGA application images

- runtime ARM software

- runtime application data (non-volatile storage)

# AM1810 Camera and Video Interfaces

The AM1810 includes an optional video port I/O interface commonly used to drive LCD screens as well as a camera input interface. These interfaces have been routed directly to the SO-DIMM-200 connector.

# **Debug Interface**

Both the JTAG interface signals for the FPGA and the JTAG signals for the AM1810 processor have been brought out to a Hirose header that is intended for use with an available Critical Link breakout adapter. This header can be removed for production units; please contact your Critical Link representative for details.

This adapter is not included with individual modules but is included with each Critical Link Development Kit that is ordered. If an adapter, Critical Link (CL) part number 80-000286, is needed please contact your Critical Link representative.

#### Software and Application Development Support

Users of the MitySOM-1810F are encouraged to develop applications using the MitySOM-1810F software development kit provided by Critical Link LLC. The development kit includes an implementation of an OpenEmbedded board support package providing an Angstrom based Linux distribution and compatible gcc compiler tool-chain with debugger.

To support rapid FPGA and applications development, netlist components - compatible with the Xilinx ISE FPGA synthesis tool – for commonly used FPGA designs and a corresponding set of Linux loadable kernel modules are included. The libraries provide the necessary functions needed to configure the MitySOM-1810F, program standalone embedded applications, and interface with the various hardware components both on the processor board as well as a custom application carrier card. The libraries include several interface "cores" – FPGA and ARM software modules designed to interface with various high performance data converter modules (ADCs, DACs, LCD and touchscreen interfaces, etc) – as well as bootloading and FLASH programming utilities.

#### **Growth Options**

The MitySOM-1810F has been designed to support several upgrade options. These options include various speed grades, memory configurations, and operating temperature specifications including commercial and industrial temperature ranges. The available options are listed in the section below containing ordering information. For additional ordering information and details regarding these options, or to inquire about a particular configuration not listed below, please contact a Critical Link sales representative.

#### ABSOLUTE MAXIMUM RATINGS

If Military/Aerospace specified cards are required, please contact the Critical Link Sales Office or unit Distributors for availability and specifications.

| Maximum Supply Voltage, Vcc | 3.5 V         |

|-----------------------------|---------------|

| Storage Temperature Range   | -65°C to 80°C |

| Shock, Z-Axis               | ±10 g         |

| Shock, X/Y-Axis             | ±10 g         |

#### **OPERATING CONDITIONS**

| Ambient Temperature | 0°C to 70°C                       |

|---------------------|-----------------------------------|

| Range Commercial    |                                   |

| Ambient Temperature | $-40^{\circ}$ C to $85^{\circ}$ C |

| Range Industrial    |                                   |

| Humidity            | 0 to 95%                          |

|                     | Non-condensing                    |

| MIL-STD-810F        | Contact Critical                  |

|                     | Link for Details                  |

#### **SO-DIMM-200 Interface Description**

The primary interface connector for the MitySOM-1810F is the SO-DIMM card edge interface.

| Table 1 SO-DIMM Pin-Out |     |                |     |     |             |  |  |

|-------------------------|-----|----------------|-----|-----|-------------|--|--|

| Pin                     | I/O | Signal         | Pin | I/O | Signal      |  |  |

| 1                       | -   | +3.3 V in      | 2   | -   | +3.3 V in   |  |  |

| 3                       | -   | +3.3 V in      | 4   | -   | +3.3 V in   |  |  |

| 5                       | -   | +3.3 V in      | 6   | -   | +3.3 V in   |  |  |

| 7                       | -   | GND            | 8   | -   | GND         |  |  |

| 9                       | -   | GND            | 10  | -   | GND         |  |  |

| 11                      | Ι   | RESET_IN#      | 12  |     | EXT_BOOT#   |  |  |

| 13                      | 0   | SATA_TX_P      | 14  | I/O | GP0_7       |  |  |

| 15                      | 0   | SATA_TX_N      | 16  | I/O | GP0_10      |  |  |

| 17                      | Ι   | SATA_RX_P      | 18  | I/O | GP0_11      |  |  |

| 19                      | Ι   | SATA_RX_N      | 20  | I/O | GP0_15      |  |  |

| 21                      | Ι   | USB0_ID        | 22  | I/O | GP0_6       |  |  |

| 23                      | I/O | USB1_D_N       | 24  | I/O | GP0_14      |  |  |

| 25                      | I/O | USB1_D_P       | 26  | I/O | GP0_12      |  |  |

| 27                      | 0   | USB0_VBUS      | 28  | I/O | GP0_5       |  |  |

| 29                      | I/O | USB0_D_N       | 30  | I/O | GP0_13      |  |  |

| 31                      | I/O | USB0_D_P       | 32  | I/O | GP0_1       |  |  |

| 33                      | 0   | USB0_DRVVBUS   | 34  | I/O | GP0_4       |  |  |

| 35                      | -   | 3V RTC Battery | 36  | I/O | GP0_3       |  |  |

| 37                      | -   | +3.3 V in      | 38  | -   | +3.3 V in   |  |  |

| 39                      | -   | +3.3 V in      | 40  | -   | +3.3 V in   |  |  |

| 41                      | -   | GND            | 42  | -   | GND         |  |  |

| 43                      | I/O | SPI1_MISO      | 44  | I/O | GP0_2       |  |  |

| 45                      | I/O | SPI1_MOSI      | 46  | I/O | GP0_0       |  |  |

| 47                      | I/O | SPI1_ENA       | 48  | I/O | GP0_8       |  |  |

| 49                      | I/O | SPI1_CLK       | 50  | I/O | GP0_9       |  |  |

| 51                      | I/O | SPI1_SCS1      | 52  | I/O | MMCSD0_DAT7 |  |  |

| 53                      | I/O | Reserved       | 54  | I/O | MMCSD0_DAT6 |  |  |

| 55                      | I/O | I2C0_SCL       | 56  | I/O | MMCSD0_DAT5 |  |  |

| 57                      | I/O | I2C0_SDA       | 58  | I/O | MMCSD0_DAT4 |  |  |

Table 1 SO-DIMM Pin-Out

Copyright © 2012, Critical Link LLC Specifications Subject to Change

| Pin | I/O        | Signal               | Pin | I/O        | Signal       |

|-----|------------|----------------------|-----|------------|--------------|

| 59  | I/O<br>I/O | UART2_TXD /          | 60  | I/O        | MMCSD0 DAT3  |

| 57  | 1/0        | I2C1_SDA             | 00  | I/ U       |              |

| 61  | I/O        | UART2 RXD / I2C1 SCL | 62  | I/O        | MMCSD0 DAT2  |

| 63  | I/O        | GND                  | 64  | I/O        | GND          |

| 65  | I/O        | UART1 TXD            | 66  | I/O        | MMCSD0 DAT1  |

| 67  | I/O        | UART1 RXD            | 68  | I/O        | MMCSD0 DAT0  |

| 69  | I/O        | MDIO_CLK             | 70  | I/O        | MMCSD0_CMD   |

| 71  | I/O        | MDIO DAT             | 72  | I/O        | MMCSD0_CLK   |

| 73  | I/O        | MII RXCLK            | 74  | I/O        | MII TXCLK    |

| 75  | I/O        | MII RXDV             | 76  | I/O        | MII TXD3     |

| 77  | I/O        | MII RXD0             | 78  | I/O        | MII TXD2     |

| 79  | I/O        | MII RXD1             | 80  | I/O        | MII TXD1     |

| 81  | I/O        | MII RXD2             | 82  | I/O        | MII TXD0     |

| 83  | I/O        | MII RXD3             | 84  | I/O        | MII TXEN     |

| 85  | -          | GND                  | 86  | -          | GND          |

| 87  | I/O        | MII_CRS              | 88  | I/O        | MII_COL      |

| 89  | I/O        | MII RXER             | 90  | I/O        | FPGA_SUSPEND |

| 91  | I/O        | B1 47 P.U17          | 92  | I/O        | B1 48 P.M14  |

| 93  | I/O        | B1_17_N.U18          | 94  | I/O        | B1 48 N.N14  |

| 95  | I/O        | B1 45 P.T17          | 96  | I/O        | B1_46_P.N15  |

| 97  | I/O<br>I/O | B1 45 N.T18          | 98  | I/O        | B1_46_N.N16  |

| 99  | I/O<br>I/O | B1 43 P.P17          | 100 | I/O        | B1 44 P.L12  |

| 101 | I/O<br>I/O | B1 43 N.P18          | 100 | I/O        | B1 44 N.L13  |

| 101 | I/O<br>I/O | B1 41 P.N17          | 102 | I/O        | B1 42 P.K12  |

| 105 | I/O<br>I/O | B1 41 N.N18          | 104 | I/O        | B1 42 N.K13  |

| 103 | -          | GND                  | 100 | -          | GND          |

| 107 | I/O        | B1 39 P.M16          | 110 | I/O        | B1 40 P.L15  |

| 111 | I/O<br>I/O | B1 39 N.M18          | 112 | I/O        | B1 40 N.L16  |

| 113 | I/O<br>I/O | B1 37 P.L17          | 112 | I/O        | B1 38 P.K15  |

| 115 | I/O        | B1 37 N.L18          | 116 | I/O        | B1 38 N.K16  |

| 117 | I/O        | B1 35 P.K17          | 118 | I/O        | B1_36_P.J13  |

| 119 | I/O        | B1 35 N.K18          | 120 | I/O        | B1 36 N.K14  |

| 121 | I/O        | B1 33 P.J16          | 120 | I/O        | B1 34 P.H15  |

| 121 | I/O        | B1 33 N.J18          | 124 | I/O        | B1 34 N.H16  |

| 125 | I/O        | B1 31 P.H17          | 126 | I/O        | B1 32 P.H13  |

| 127 | I/O        | B1_31_N.H18          | 128 | I/O        | B1_32_N.H14  |

| 129 | -          | GND                  | 130 | -          | GND          |

| 131 | I/O        | B1 29 P.G16          | 132 | I/O        | B1 30 P.F15  |

| 133 | I/O        | B1_29_N.G18          | 134 | I/O        | B1_30_N.F16  |

| 135 | I/O<br>I/O | B1 27 P.F17          | 136 | I/O        | B1 28 P.H12  |

| 133 | I/O<br>I/O | B1_27_N.F18          | 138 | I/O        | B1_28_N.G13  |

| 139 | I/O<br>I/O | B1 25 P.E16          | 140 | I/O        | B1 26 P.F14  |

| 141 | I/O<br>I/O | B1 25 N.E18          | 142 | I/O        | B1_26_N.G14  |

| 141 | I/O<br>I/O | B1_23_P.D17          | 144 | I/O        | B0 24 P.F13  |

| 145 | I/O<br>I/O | B1_23_N.D18          | 146 | I/O        | B0 24 N.E13  |

| 143 | I/O<br>I/O | B1 21 P.C17          | 148 | I/O        | B0 22 P.D14  |

| 147 | I/O<br>I/O | B1 21 N.C18          | 140 | I/O<br>I/O | B0 22 N.C14  |

| 151 | -          | GND                  | 150 | -          | GND          |

| 153 | I/O        | B0 19 P.B16          | 152 | I/O*       | B0 20 P.F12* |

| 155 | I/O<br>I/O | B0_19_N.A16          | 154 | I/O*       | B0 20 N.E12* |

| 155 | I/O<br>I/O | B0_17_P.C15          | 150 | I/O*       | B0 18 P.D12* |

| 157 | I/U        | D0_17_1.013          | 100 | I/U        | DV_10_1.D12  |

Copyright © 2012, Critical Link LLC Specifications Subject to Change

| Pin                                                                         | I/O               | Signal               | Pin    | I/O        | Signal                       |  |

|-----------------------------------------------------------------------------|-------------------|----------------------|--------|------------|------------------------------|--|

| 159                                                                         | <u>I/O</u><br>I/O | B0 17 N.A15          | 160    | I/O*       | B0 18 N.C12*                 |  |

| 159                                                                         | I/O<br>I/O        | B0 15 P.B14          | 162    | I/O*       | B0_16_P.F11*                 |  |

| 163                                                                         | I/O<br>I/O        | B0_15_N.A14          | 162    | I/O*       | B0_16_N.E11*                 |  |

| 165                                                                         | I/O<br>I/O        | B0_13_P.C13          | 166    | I/O<br>I/O | B0_10_R.E11<br>B0_14_P.D11   |  |

| 167                                                                         | I/O<br>I/O        | B0 13 N.A13          | 168    | I/O<br>I/O | B0 14 N.C11                  |  |

| 167                                                                         | I/O<br>I/O        | B0 11 P.B12          | 170    | I/O*       | B0 12 P.E7*                  |  |

| 171                                                                         | I/O<br>I/O        | B0_11_N.A12          | 170    | I/O*       | B0 12 N.E8*                  |  |

| 171                                                                         | -                 | GND                  | 172    | -          | GND                          |  |

| 175                                                                         | I/O               | B0 9 P.B11           | 176    | I/O        | B0 10 P.D9                   |  |

| 173                                                                         | I/O               | B0 9 N.A11           | 178    | I/O        | B0 10 N.C9                   |  |

| 179                                                                         | I/O               | B0_7_P.C10           | 180    | I/O        | B0_8_P.D8                    |  |

| 181                                                                         | I/O               | B0 7 N.A10           | 182    | I/O        | B0 8 N.C8                    |  |

| 183                                                                         | I/O               | B0 5 P.B9            | 184    | I/O        | B0 6 P.D6                    |  |

| 185                                                                         | I/O               | B0 5 N.A9            | 186    | I/O        | B0 6 N.C6                    |  |

| 187                                                                         | I/O               | B0 3 P.B8            | 188    | I/O        | B0 4 P.B6                    |  |

| 189                                                                         | I/O               | B0_3_N.A8            | 190    | I/O        | B0_4_N.A6                    |  |

| 191                                                                         | I/O               | B0_1_P.C7            | 192    | I/O        | B0_2_P.C5                    |  |

| 193                                                                         | I/O               | B0_1_N.A7            | 194    | I/O        | B0_2_N.A5                    |  |

| 195                                                                         | -                 | GND                  | 196    | -          | GND                          |  |

| 197                                                                         | -                 | VCCO_1               | 198    | -          | VCCO_0                       |  |

| 199                                                                         | -                 | VCCO_1               | 200    | -          | VCCO_0                       |  |

| * The                                                                       | Xilinx            | 6SLX45 FPGA does not | t bond | I/O Bu     | uffers to balls E7, E8, F11, |  |

|                                                                             |                   |                      |        |            | sed for this module. For     |  |

| MitySOM-1810F configurations using this FPGA option, these edge             |                   |                      |        |            |                              |  |

| connector signals should be treated as no-connects and will not function as |                   |                      |        |            |                              |  |

|                                                                             | I/O lir           |                      |        |            |                              |  |

The signal group description for the above pins is included in Table 2

| Table 2 Signal Group Description |     |                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|----------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Signal / Group                   | I/O | Description                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 3.3 V in                         | N/A | 3.3 volt input power referenced to GND.                                                                                                                                                                                                                                                                                                                 |  |  |  |

| EXT_BOOT#                        | Ι   | Bootstrap configuration pin. Pull low to configure                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                  |     | booting from external UART1.                                                                                                                                                                                                                                                                                                                            |  |  |  |

| RESET_IN#                        | Ι   | Manual Reset. When pulled to GND for a                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                  |     | minimum of 1 usec, resets the DSP processor.                                                                                                                                                                                                                                                                                                            |  |  |  |

| SPI_XXXX                         | I/O | The pins with an SPI_ prefix are direct<br>connections to the AM1810 pins supporting the<br>SPI1 interface. The SPI1_CLK, SPI1_ENA,<br>SPI1_MISO, SPI1_MOSI pins must remain<br>configured for the SPI function in order to support<br>interfacing to the on-board SPI boot ROM. For<br>details please refer to the AM1810 processor<br>specifications. |  |  |  |

| MII_XXXX                         | I/O | The pins with an MII_ prefix are direct                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                  |     | connections to the AM1810 pins supporting the                                                                                                                                                                                                                                                                                                           |  |  |  |

| Signal / Group | I/O | Description                                        |

|----------------|-----|----------------------------------------------------|

|                |     | media independent interface (MII) function. The    |

|                |     | MII pins provide multiplex capability and may      |

|                |     | alternately be used as UART, GPIO, and SPI         |

|                |     | control pins. For details please refer to the      |

|                |     | AM1810 processor specification.                    |

| MDIO_XX        | I/O | The MDIO_CLK and MDIO_DAT signals are              |

|                |     | direct connects to the corresponding MDIO          |

|                |     | signals on the AM1810 processor. These pins        |

|                |     | may be configured for GPIO.                        |

| GP0_X          | IO  | General Purpose / multiplexed pins. These pins are |

|                |     | direct connects to the corresponding GP0[X] pins   |

|                |     | on the AM1810 processor. The include support       |

|                |     | for the McASP, general purpose I/O, UART flow      |

|                |     | control, and McBSP 1. For details please refer to  |

|                |     | the AM1810 processor specifications.               |

| SATA_TX_P/N    | 0   | These pins are direct connects to the AM1810       |

|                |     | SATA_TX differential Serial ATA controller pins.   |

| SATA_RX P/N    | I   | These pins are direct connects to the AM1810       |

|                |     | SATA_RX differential Serial ATA controller pins.   |

| GND            | N/A | System Digital Ground.                             |

| BX_Y_P.ZZ,     | IO  | FPGA I/O pins. These pins are routed directly to   |

| BX_Y_N.ZZ      |     | FPGA pins ZZ. The "X" indicates which FPGA         |

|                |     | bank the pin is allocated. The bank is either 0 or |

|                |     | 1. The FPGA fabric supports routing pins in        |

|                |     | differential pairs, the Y_P and Y_N portion of the |

|                |     | name indicates the pair number and polarity. The   |

|                |     | pins have been routed in pairs with phase matched  |

|                |     | line lengths.                                      |

| VCCO_X         | Ι   | FPGA Bank interface power input. These pins        |

|                |     | must be tied to the desired voltage used for the   |

|                |     | FPGA Bank 0 or 1 interface pins. Please refer to   |

|                |     | the VCCO input pin specifications for the Xilinx   |

|                |     | Spartan 6 family of devices for further            |

|                |     | information. Typical values are 3.3V and 2.5       |

|                |     | volts.                                             |

| USB0_XXXX,     | I/O | The USBN_ prefixed pins are direct connects to     |

| USB1_XXXX      |     | the corresponding pins on the AM1810 processor.    |

|                |     | For details please refer to the AM1810 processor   |

|                |     | specifications.                                    |

#### **DEBUG INTERFACE**

Below is the pin-out for the Hirose 31 pin header (DF9-31P-1V(32)) that interfaces with an available adapter board, CL part number 80-000286, to debug the AM1810 and FPGA.

#### **Debug Interface Connector Description (J2)**

| Table 3 OMAP-L138 Hirose Connector |     |        |     |     |                    |  |  |  |

|------------------------------------|-----|--------|-----|-----|--------------------|--|--|--|

| Pin                                | I/O | Signal | Pin | I/O | Signal             |  |  |  |

| 1                                  | -   | GND    | 2   | 0   | OMAP EMU1          |  |  |  |

| 3                                  | -   | GND    | 4   | 0   | OMAP EMU0          |  |  |  |

| 5                                  | -   | GND    | 6   | Ι   | OMAP TCK           |  |  |  |

| 7                                  | -   | GND    | 8   | 0   | OMAP RTCK          |  |  |  |

| 9                                  | -   | GND    | 10  | 0   | OMAP TDO           |  |  |  |

| 11                                 | -   | GND    | 12  | -   | OMAP VCC / 3.3V    |  |  |  |

| 13                                 | -   | GND    | 14  | Ι   | OMAP TDI           |  |  |  |

| 15                                 | -   | GND    | 16  | Ι   | OMAP TRST          |  |  |  |

| 17                                 | -   | GND    | 18  | Ι   | OMAP TMS           |  |  |  |

| 19                                 | -   | GND    | 20  | -   | GND                |  |  |  |

| 21                                 | -   | GND    | 22  | 0   | FPGA VREF / VCCAUX |  |  |  |

| 23                                 | -   | GND    | 24  | Ι   | FPGA TMS           |  |  |  |

| 25                                 | -   | GND    | 26  | Ι   | FPGA TCK           |  |  |  |

| 27                                 | -   | GND    | 28  | 0   | FPGA TDO           |  |  |  |

| 29                                 | -   | GND    | 30  | Ι   | FPGA TDI           |  |  |  |

| 31                                 | -   | GND    |     |     |                    |  |  |  |

| Table 3 | OMAP-L138   | Hirose    | Connector |

|---------|-------------|-----------|-----------|

| I ant J | UNIAI -LIJU | J III USU | Connector |

# ELECTRICAL CHARACTERISTICS

#### Table 4: Electrical Characteristics

| Symbol  | Parameter                                                                                                                                                                                                                               | Conditions      | Min | Тур | Max | Units |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|-------|--|

|         |                                                                                                                                                                                                                                         |                 |     |     |     |       |  |

| V33     | Voltage supply, 3.3 volt input.                                                                                                                                                                                                         |                 | 3.2 | 3.3 | 3.4 | Volts |  |

| 133     | Quiescent Current draw, 3.3 volt input                                                                                                                                                                                                  |                 |     | TBS | TBS | mA    |  |

| I33-max | Max current draw, positive 3.3 volt input.                                                                                                                                                                                              |                 |     | TBS | TBS | mA    |  |

| FCPU    | CPU internal clock Frequency (PLL output)                                                                                                                                                                                               |                 | 25  | 375 | 375 | MHz   |  |

| FEMIF   | EMIF bus frequency                                                                                                                                                                                                                      | Must be 1/2 CPU | -   | 100 | -   | MHz   |  |

|         | <ol> <li>Power utilization of the MitySOM-1810F is heavily dependant on end-user application. Major<br/>factors include: ARM CPU PLL configuration, DSP Utilization FPGA utilization, and external<br/>DDR2 RAM utilization.</li> </ol> |                 |     |     |     |       |  |

#### **ORDERING INFORMATION**

The following table lists the standard module configurations. For shipping status, availability, and lead time of these or other configurations please contact your Critical Link representative.

| Model          | ARM Speed | FPGA   | NOR<br>Flash | NAND Flash | RAM   | Operating<br>Temp                 |

|----------------|-----------|--------|--------------|------------|-------|-----------------------------------|

| 1810-DG-225-RC | 375 MHz   | 6SLX16 | 8MB          | 256MB      | 128MB | $0^{\circ}$ C to $70^{\circ}$ C   |

| 1810-DG-225-RI | 375 MHz   | 6SLX16 | 8MB          | 256MB      | 128MB | $-40^{\circ}$ C to $85^{\circ}$ C |

| Table  | 5: | Standard | Model | Numbers      |

|--------|----|----------|-------|--------------|

| I unic | ~. | Standara | mouch | 1 (unitoer b |

#### MECHANICAL INTERFACE

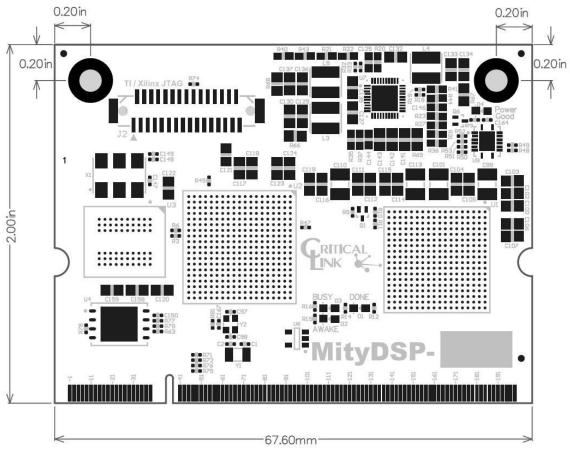

A mechanical outline of the MitySOM-1810F is illustrated in Figure 2, below.

Figure 2 MitySOM-1810F Mechanical Outline

# **REVISION HISTORY**

| Date        | Change Description                                      |

|-------------|---------------------------------------------------------|

| 23-FEB-2012 | Preliminary Draft, Updates and Release                  |

| 11-DEC-2012 | Update Debug Header information, added MIL-STD-810F and |

|             | Up To notation for RAM and NAND                         |

| 5-MAR-2014  | Update MitySOM product name.                            |

|             |                                                         |

|             |                                                         |

|             |                                                         |

|             |                                                         |

|             |                                                         |

|             |                                                         |

|             |                                                         |

|             |                                                         |